原文地址:https://blog.csdn.net/muxiqingyang/article/details/6615199

处理器上有一套完整的协议,来保证Cache一致性。比较经典的Cache一致性协议当属MESI协议,奔腾处理器有使用它,很多其他的处理器都是使用它的变种。

单核Cache中每个Cache line有2个标志:dirty和valid标志,它们很好的描述了Cache和Memory(内存)之间的数据关系(数据是否有效,数据是否被修改),而在多核处理器中,多个核会共享一些数据,MESI协议就包含了描述共享的状态。

在MESI协议中,每个Cache line有4个状态,可用2个bit表示,它们分别是:

|

状态 |

描述 |

|

M(Modified) |

这行数据有效,数据被修改了,和内存中的数据不一致,数据只存在于本Cache中。 |

|

E(Exclusive) |

这行数据有效,数据和内存中的数据一致,数据只存在于本Cache中。 |

|

S(Shared) |

这行数据有效,数据和内存中的数据一致,数据存在于很多Cache中。 |

|

I(Invalid) |

这行数据无效。 |

MESI状态

M(Modified)和E(Exclusive)状态的Cache line,数据是独有的,不同点在于M状态的数据是dirty的(和内存的不一致),E状态的数据是clean的(和内存的一致)。

S(Shared)状态的Cache line,数据和其他Core的Cache共享。只有clean的数据才能被多个Cache共享。

I(Invalid)表示这个Cache line无效。

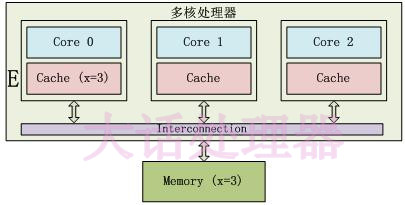

E状态示例如下:

E状态

只有Core 0访问变量x,它的Cache line状态为E(Exclusive)。

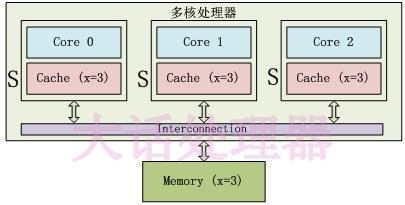

S状态示例如下:

S状态

3个Core都访问变量x,它们对应的Cache line为S(Shared)状态。

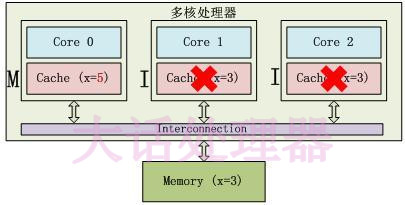

M状态和I状态示例如下:

M状态和I状态

Core 0修改了x的值之后,这个Cache line变成了M(Modified)状态,其他Core对应的Cache line变成了I(Invalid)状态。

在MESI协议中,每个Cache的Cache控制器不仅知道自己的读写操作,而且也监听(snoop)其它Cache的读写操作。每个Cache line所处的状态根据本核和其它核的读写操作在4个状态间进行迁移。

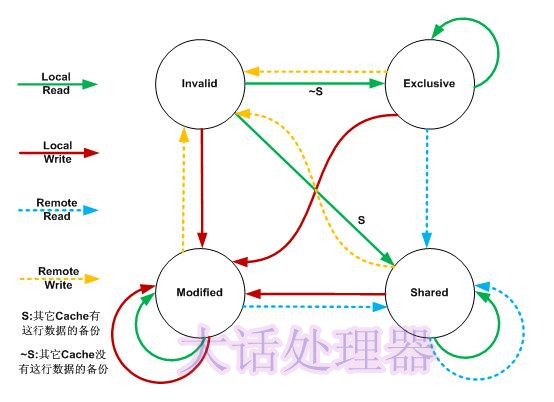

MESI协议状态迁移图如下:

MESI协议状态迁移图

在上图中,Local Read表示本内核读本Cache中的值,Local Write表示本内核写本Cache中的值,Remote Read表示其它内核读其它Cache中的值,Remote Write表示其它内核写其它Cache中的值,箭头表示本Cache line状态的迁移,环形箭头表示状态不变。

当内核需要访问的数据不在本Cache中,而其它Cache有这份数据的备份时,本Cache既可以从内存中导入数据,也可以从其它Cache中导入数据,不同的处理器会有不同的选择。MESI协议为了使自己更加通用,没有定义这些细节,只定义了状态之间的迁移,下面的描述假设本Cache从内存中导入数据。

MESI状态之间的迁移过程如下:

|

当前状态 |

事件 |

行为 |

下一个状态 |

|

I(Invalid) |

Local Read |

如果其它Cache没有这份数据,本Cache从内存中取数据,Cache line状态变成E; 如果其它Cache有这份数据,且状态为M,则将数据更新到内存,本Cache再从内存中取数据,2个Cache 的Cache line状态都变成S; 如果其它Cache有这份数据,且状态为S或者E,本Cache从内存中取数据,这些Cache 的Cache line状态都变成S |

E/S |

|

Local Write |

从内存中取数据,在Cache中修改,状态变成M; 如果其它Cache有这份数据,且状态为M,则要先将数据更新到内存; 如果其它Cache有这份数据,则其它Cache的Cache line状态变成I |

M |

|

|

Remote Read |

既然是Invalid,别的核的操作与它无关 |

I |

|

|

Remote Write |

既然是Invalid,别的核的操作与它无关 |

I |

|

|

E(Exclusive) |

Local Read |

从Cache中取数据,状态不变 |

E |

|

Local Write |

修改Cache中的数据,状态变成M |

M |

|

|

Remote Read |

数据和其它核共用,状态变成了S |

S |

|

|

Remote Write |

数据被修改,本Cache line不能再使用,状态变成I |

I |

|

|

S(Shared) |

Local Read |

从Cache中取数据,状态不变 |

S |

|

Local Write |

修改Cache中的数据,状态变成M, 其它核共享的Cache line状态变成I |

M |

|

|

Remote Read |

状态不变 |

S |

|

|

Remote Write |

数据被修改,本Cache line不能再使用,状态变成I |

I |

|

|

M(Modified) |

Local Read |

从Cache中取数据,状态不变 |

M |

|

Local Write |

修改Cache中的数据,状态不变 |

M |

|

|

Remote Read |

这行数据被写到内存中,使其它核能使用到最新的数据,状态变成S |

S |

|

|

Remote Write |

这行数据被写到内存中,使其它核能使用到最新的数据,由于其它核会修改这行数据, 状态变成I |

I |

MESI状态迁移

AMD的Opteron处理器使用从MESI中演化出的MOESI协议,O(Owned)是MESI中S和M的一个合体,表示本Cache line被修改,和内存中的数据不一致,不过其它的核可以有这份数据的拷贝,状态为S。

Intel的core i7处理器使用从MESI中演化出的MESIF协议,F(Forward)从Share中演化而来,一个Cache line如果是Forward状态,它可以把数据直接传给其它内核的Cache,而Share则不能。

相关推荐

5-3JMM-CPU缓存一致性协议MESI.mp4

带有高速缓存的CPU执行计算的流程). 程序以及数据被加载到主内存,. 指令和数据被加载到CPU的高速缓存-. CPU执行指令,把结果写到高速缓存.. 高速缓存

MESI协议.xmind

15418缓存模拟器这是一个缓存一致性协议模拟器,具有MSI,MESI和MOESI协议。 此外,我们实现了包含回写缓冲区以及非原子总线事务的功能,从而实现了更逼真的仿真。

MESI

缓存一致性 为基于总线的广播系统实现 MI、MSI、MESI、MOSI、MOESI 和 MOESIF 协议。

Multi2sim是多核系统结构仿真器,支持多级Cache,支持定制不同的层次结构,其中一致性协议用MESI协议实现。网络目前只支持Bus和P2P。

– Cache Coherence算法 (MESI, MOESI); – CPU Memory Ordering模型 (Atomic,Reorder,Memory Barrier (Compiler, CPU),Lock Instruction,Load Acquire/Store Release); – 并发程序设计 (实现一个Spinlock,...

• 基于MESI缓存⼀一致性协议 如果不声明volatile,变量装载到本地变量 中,或者cpu cache中,多线程下很容易导 致状态不⼀一致。 • 声明了volatile,每次访问的都是主存中的数 据,⼀一致性能提升,但是还是不可靠...

缓存一致性协议 (MESI) modify :修改状态,表示共享数据只缓存在当前 CPU 并且是修改状态,也就是缓存的数据与主内存中不一致 shared:共享状态,多个 CPU 缓存中的内容与主内存中内容一致 invalid :失效状态,...

大家都学过计算机体系结构吧,里面有个MESI协议,是不是有点印象,这个就是我用VB做的一个演示程序。是源码哦

第2节并发基础2.1CPU多级缓存--缓存一致性·缓存一致性(MESI,Cache line的四种状态)M:Modified,被修改E:Exclusive,独享

MESI电子商务 MESI项目 介绍 项目管理: Trello 返回: Java SPRING-Thymeleaf 前: HTML CSS Boostrap JS 备份管理: GitHub SGBD: MySQL 开发服务器 可访问suivante:

详细的讲述了并发、高并发、CPU Cache、CPU多级缓存、CPU多级缓存 - 缓存一致性(MESI)、CPU多级缓存-乱序执行优化、Java内存模型(Java Memory Model,JMM)、并发的优势和风险...等等图文并茂详解

blm304 维里·哈贝莱西梅西(VeriHaberleşmesi)

Multi-level inclusive cache hierarchy with the directory-based MESI coherence protocol; Simple cycle-accurate DRAM controller model; Various kinds of static and dynamic branch predictors, ...

计算机组织与体系结构性能设计(第6版) ...18.3 高速缓存一致性和MESI协议 18.4 机群系统 18.5 非对称存储器存取 18.6 向量计算 18.7 参考文献 18.8 关键词、复习题和习题 附录 词汇表 参考文献 索引

L2 cache sub-systems and the MESI cache consistency protocol. Pipelined burst cache. 8. All in one—the i486. Pins and signals of the i486. Internal structure of the i486. RISC or CISC. ...

利用AFLP技术,选择EcoRI/MesI酶切组合,从48对EcoRI+3/MesI+3引物组合中筛选出6对引物进行选择性扩增,检测了鸢尾属植物26个样品基因组的DNA多态性,共扩增出536个遗传位点,并通过Jaccard的方法将电泳谱带矩阵转化...

法院审判简单易行:-原始的可见之光,假的原始之作,可见的可见之物(vos yeux disentdéjàmerci),-乐团之选,以及集体之声Jaune,公民投票组织,海关总署,负责人(加格罗斯),-消息和指导书,补充条款,同意书...